Fabian Schätzle - DR project

Inter-chiplet communication for next-gen HPC processors

Doctoral Researcher: Fabian Schätzle

Local ZEA-2 Supervisor: Stefan Heinen

Academic Supervisor: Estela Suarez, Jülich Supercomputing Centre (JSC)

Topic: Neuromorphic Computing

Research Field: Information

High-performance computing (HPC) leverages high amount of processing cores, massive data storage and high-speed interconnects to solve complex problems e.g. Artificial intelligence.

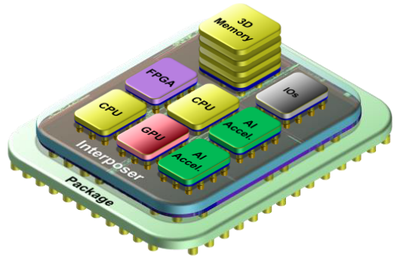

Manufacturing such large chips is not economical since this process is not perfect. To reduce costs one can split up a chip into multiple smaller chiplets and integrate them together with advanced packaging technologies (Figure1). This also enables the integration of chiplets from different vendors providing promising heterogeneous solutions for enhancing scalable design, reducing development cost, increasing reusability and performance and improving power consumption.

The scope of the PhD project aims at providing a modeling solution for exploring future chiplet-to-chiplet architectures and providing quantitative analyses of the optimal architectures to match the requirements and needs of HPC applications. To model the chip, an industry standard system-level design language called SystemC is used. Due to the lack of free and configurable processor models in SystemC, first we focus on finding an efficient solution for integrating SystemC and Gem5 simulator. This finding is used to develop a chiplet-to-chiplet interconnection model and integrating it with other discrete chiplet models (processors or memory devices) available either with Gem5 or SystemC.

Second, we use the model to demonstrate a use-case study. The research then will step on exploring the ARM-based chiplet systems via evaluations for different memory access pattern testbeds and a set of relevant HPC applications and benchmarks.

Expected outcome is to identify the optimization solutions through quantitatively analyzing different design trade-offs for performance, power consumption, and hardware cost.

References

[1] P. Vivet et al., "IntAct: A 96-Core Processor With Six Chiplets 3D-Stacked on an Active Interposer With Distributed Interconnects and Integrated Power Management," in IEEE Journal of Solid-State Circuits, vol. 56, no. 1, pp. 79-97, Jan. 2021, doi: 10.1109/JSSC.2020.3036341.

- Central Institute of Engineering, Electronics and Analytics (ZEA)

- Electronic Systems (ZEA-2)

Room 200F