IC Development

About

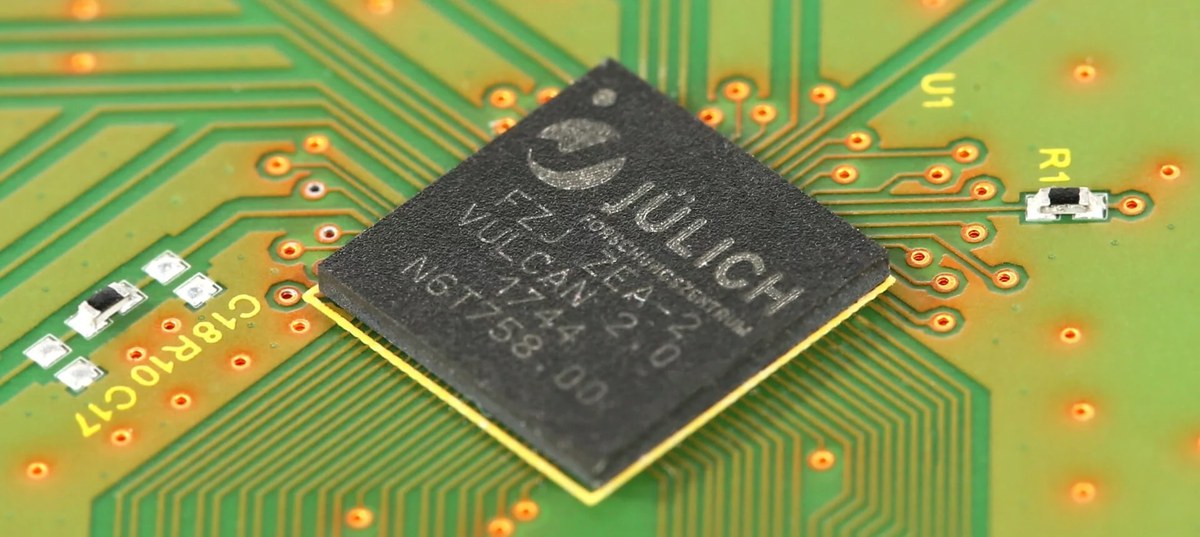

The team "IC Development" focuses on the development of integrated circuits. The team combines the complete development chain from concept to circuit design and physical implementation. Modern and industrially established CMOS technology nodes are used to leverage the full potential of scalable electronics for science and research.

Research Topics

Our methods

- Concepts and Architectures of ICs

- Full-Custom, Digital and Mixed-Signal Designs

- Physical Implementation and Signoff

- Virtual Prototyping with FPGAs

- Pre-Silicon Verification and Post-Silicon Validation

Mainly Used Technology Nodes:

- 22nm Silicon-on-Isolator (SOI)

- 28nm Bulk CMOS

- 65nm Bulk CMOS

Current Projects

Our team is mainly active in the following projects, mostly to contribute in the design process of an integrated circuit:

- Neurotec II

- New Generation ADC 28nm

- QSolid

- SemiQuBiC

Meet the team

Cadence Academic Network Activities

The academic network was launched in 2007 by Cadence® Europe. The aim was to promote the proliferation of leading-edge technologies and methodologies at universities renowned for their engineering and design excellence. A knowledge network among selected European universities, research institutes, industry advisors and Cadence was established to facilitate the sharing of technology expertise in the areas of verification, design and implementation of microelectronic systems. The Central Institute of Engineering, Electronics and Analytics ZEA-2: Electronic Systems is a member since 2013.

We use Cadence software for research:

Our main research topics are design and verification of System-on-aChip (SoC) solutions for the various research applications of the Forschungszentrum Juelich GmbH. For all these topics we rely on various tools from the Cadence product portfolio, mainly including the Virtuoso® Custom Design Platform, Spectre®, Genus™ Synthesis Solution, Innovus™ Implementation System, the silicon signoff tools Tempus™ and Voltus™, and Xcelium™ Logic Simulation.

Cadence, the Cadence logo, Encounter, Incisive, Spectre and Virtuoso are registered trademarks of Cadence Design Systems, Inc., 2655 Seely Avenue, San Jose, CA 95134. All others are the property of their respective holders.